文章內容

實體設計(Physical design)

❒ 實體設計的定義

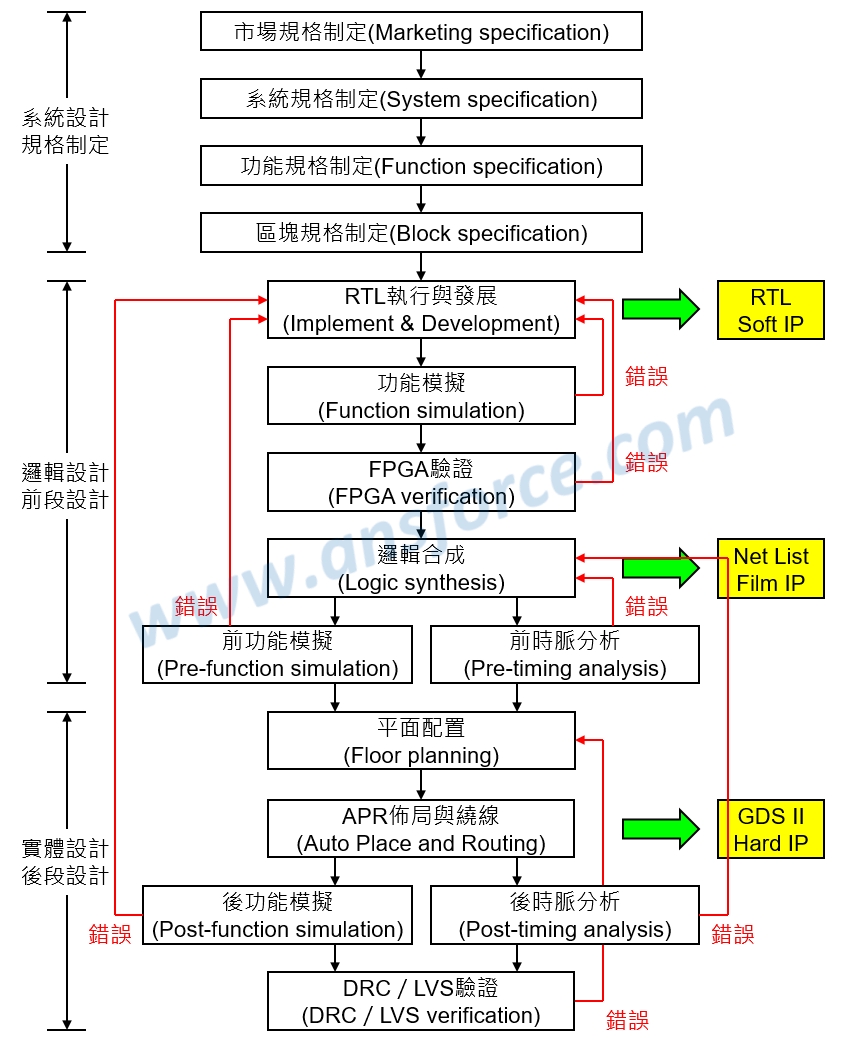

實體設計的主要工作是在將邏輯閘(Gate)轉換成電晶體(CMOS),並且將這些電晶體(CMOS)真正配置在矽晶片上的「實際位置」,再使用金屬導線連接起來形成「實際連線」,詳細的設計流程如<圖一>所示。

圖一 數位積體電路的設計流程。

❒ 平面配置(Floor planning)

平面配置的主要目的在決定每個「功能單元(Function unit)」與「區塊(Block)」在矽晶片中的實際位置,例如:CPU包含控制單元、算術邏輯運算單元、記憶體單元、浮點運算單元等不同功能單元的實際位置。此外,每個功能單元又可以再細分為許多區塊,例如:CPU的算術邏輯運算單元可能包含加法區塊、減法區塊、乘法區塊與除法區塊,這些不同區塊的實際位置。

平面配置的動作與蓋大樓所畫的建築設計圖(藍圖)很類似,在建築設計圖中必須先決定大樓的教室、辦公室、廁所、樓梯等要配置在什麼位置;IC設計圖也必須先決定每個功能單元與區塊在矽晶片中的實際位置。知識力www.ansforce.com。

❒ APR佈局與繞線(APR:Auto Place and Routing)

「佈局(Place)」的主要目的在決定積體電路(IC)中每個邏輯閘以及其所代表的電晶體的實際位置,「繞線(Routing)」的主要目的在決定積體電路(IC)中的電晶體與電晶體之間的實際連線。將邏輯合成以後所得到的邏輯設計圖載入APR佈局與繞線所使用的電子設計自動化工具(EDA tool),經過電腦輔助設計將「邏輯設計圖」轉換成相對應的數十層「光罩圖形」,不同層的光罩圖形以不同的顏色表示,光罩圖形是一個具有價值的設計結果,也是重要的智慧財產權(IP),稱為「Hard IP」,大家應該也猜得到,因為光罩是具有實體的東西,所以稱它為「硬體(Hard)」。APR佈局與繞線所使用的電子設計自動化工具很多,常見的有:益華科技(Candence)所銷售的「SoC Encounter」、新思科技(Sysnopsys)所銷售的「Astro」。

❒ 後功能模擬與前時脈分析

➤後功能模擬(Post-function simulation):主要在驗證上述佈局與繞線是否正確,如果正確則進行下一步「DRC/LVS驗證」;如果錯誤則返回「RTL執行與發展」重新修改程式,如<圖一>所示。

➤後時脈分析(Post-timing analysis):主要在驗證上述佈局與繞線是否可以在產品所要求的工作頻率下正確地運作,如果可以則進行下一步「DRC/LVS驗證」;如果錯誤則返回「邏輯合成」重新修改的邏輯閘位置與邏輯連線。

❒ DRC/LVS驗證(Design Rule Check/Layout-versus-Schematic verification)

在光罩圖形設計完成準備送進光罩與製造廠之前,還必須經過最後的檢查手續,以確定光罩圖形正確無誤,檢查的項目包括:

➤DRC驗證(DRC:Design Rule Check):主要在檢查光罩圖形是否符合晶圓代工廠所提供的各項製程規格,例如:閘極寬度、金屬線寬等,假設這座晶圓代工廠提供的製程是10nm(奈米),則光罩圖形的「閘極寬度」一定不能小於10nm,否則這座晶圓廠便無法生產。這就好像營造廠所使用的磚頭寬度是10公分,可是建築設計圖上所畫的牆壁寬度卻只有9公分,每塊磚頭都要敲掉1公分,這不是在找營造廠的麻煩嗎?

➤LVS驗證(LVS:Layout versus Schematic):主要在檢查晶片上所有電晶體(CMOS)的「實際位置」與的「實際連線」是否正確,如果正確則送入光罩廠製作光罩;如果錯誤則返回「平面配置」重新修改光罩圖形。DRC/LVS驗證所使用的電子設計自動化工具很多,常見的有:益華科技(Candence)所銷售的「Assura」、明導科技(Mentor)所銷售的「Calibre」等。

將光罩圖形送進光罩廠製作光罩的動作稱為「Tape out」,當IC設計公司將某一個積體電路(IC)「Tape out」,表示已經完成了所有積體電路設計的工作,但是仍然不能保證這個積體電路(IC)一定可以正常工作,必須將製作完成的積體電路送回IC設計公司連接到真實的系統上進行許多實際的測試與分析,然後修改光罩圖形再製作新的光罩與積體電路(IC),如此反覆進行(一般至少要三次),直到通過所有測試與分析才算真正「量產(Mass production)」。

❒ 光罩圖形與光罩的製作

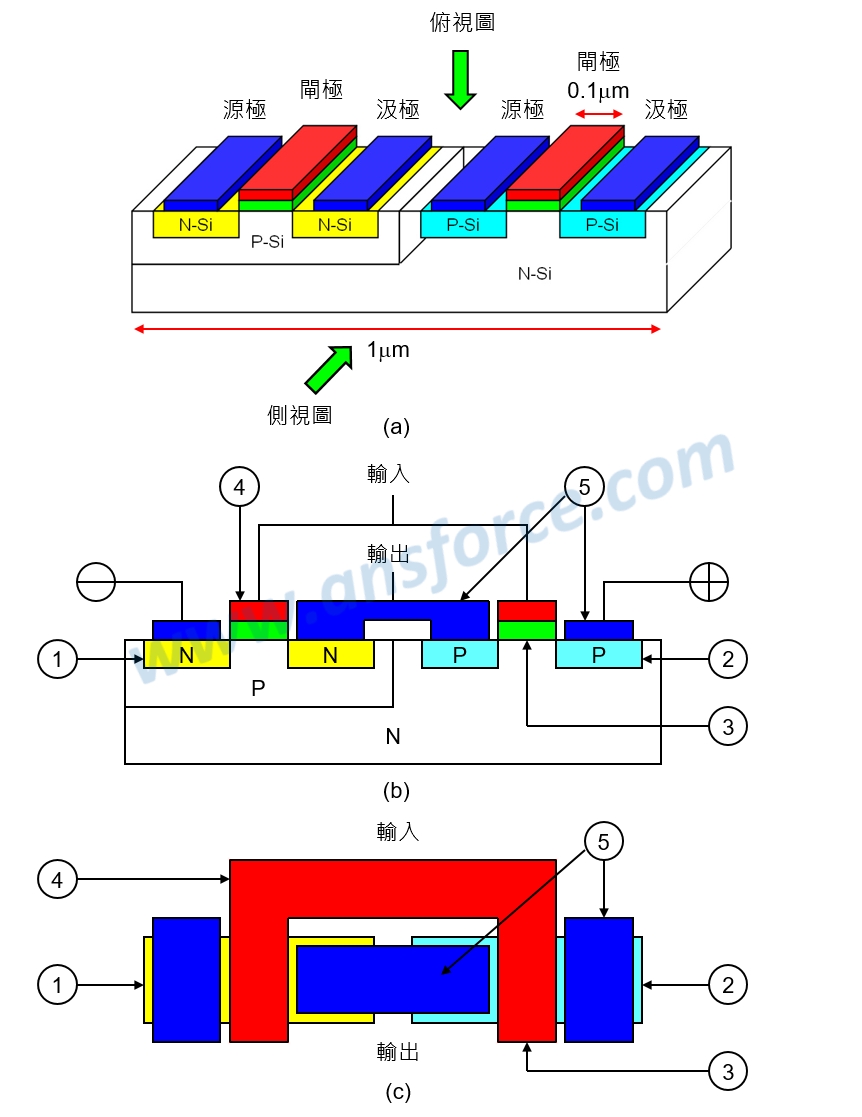

<圖二(a)>為一個CMOS的外觀結構圖,其前視圖(由前往後看)如<圖二(b)>所示,而其府視圖(由上往下看)如<圖二(c)>所示,府視圖其實就是「光罩圖形」。換句話說,光罩圖形其實就是數百萬個「電晶體(CMOS)」在矽晶片中排列組合後的「府視圖」。

由<圖二(b)>中可以看出,要製作一個CMOS總共有5層,由下而上分別為第1層:NMOS的N型水溝;第2層:PMOS的P型水溝;第3層:中央氧化物(氧化矽);第4層:中央多晶矽(Poly silicon);第5層:金屬導線。在晶圓廠中實際將CMOS製作在矽晶片上時,必須按照這個順序由下往上一層一層地製作,就好像在地球表面蓋房子一樣,必須由下往上一層樓一層樓施工。這5層重疊起來以後的府視圖分別可以對應到<圖二(c)>的光罩圖形中,而且不同層的圖形會使用不同的顏色來表示,以避免混淆。

圖二 一個CMOS的外觀與光罩圖形。

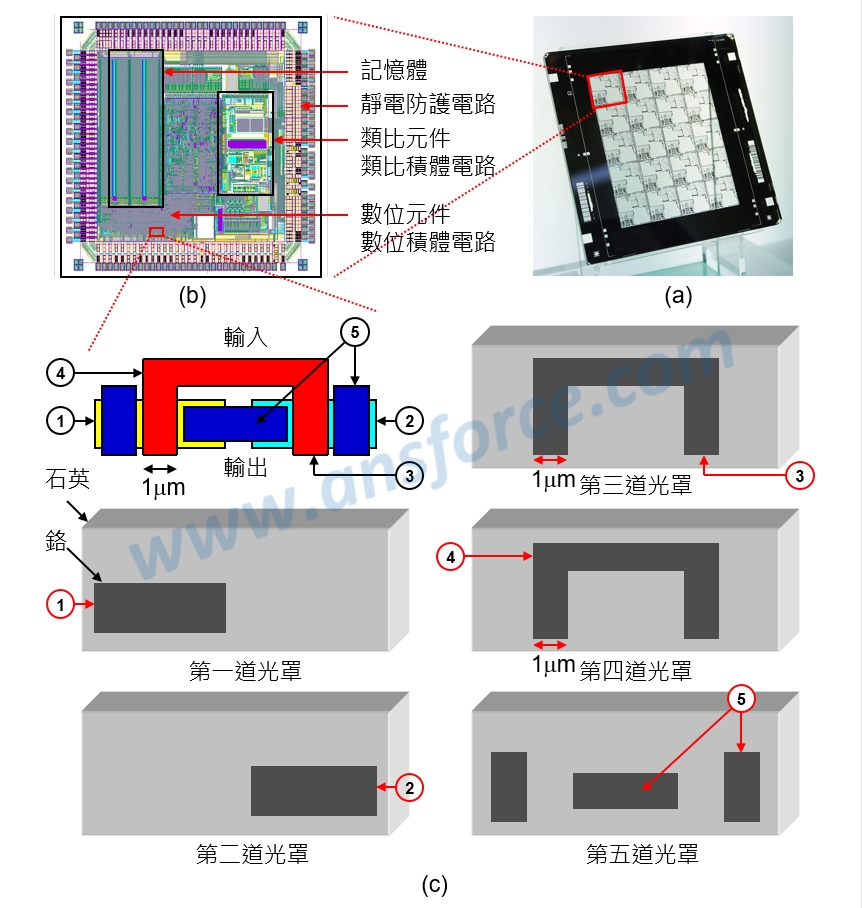

❒ 光罩製作

在實際製作光罩時,一個光罩上會重覆許多同一個晶片的光罩圖形,這樣才能減少曝光的次數,如<圖三(a)>中一個光罩重覆了相同16個晶片的光罩圖形,每一個光罩圖形有數百萬個CMOS,如<圖三(b)>所示,我們取出一個CMOS的圖形放大來看,如<圖三(c)>所示,由下而上依序有五片石英來刻畫不同層的光罩圖形,每一片石英稱為「一道光罩」,總共有五道光罩:

➤第一道光罩:第一片石英用來製作CMOS第1層「NMOS的N型水溝」。

➤第二道光罩:第二片石英用來製作CMOS第2層「PMOS的P型水溝」。

➤第三道光罩:第三片石英用來製作CMOS第3層「中央氧化物(氧化矽)」。

➤第四道光罩:第四片石英用來製作CMOS第4層「中央多晶矽」。

➤第五道光罩:第五片石英用來製作CMOS第5層「金屬導線」。

再提醒大家一次,<圖二>與<圖三(c)>所示的光罩圖形只有「一個CMOS」,實際的一個矽晶片上會有「數百萬個CMOS」,每片石英上只有一道光罩圖形,每一道光罩圖形都是一大堆密密麻麻(數百萬個CMOS)的幾何圖形,而且一般積體電路(IC)的光罩圖形不只五層而已,圖中只畫出了五道光罩來說明。

圖三 光罩圖形。

資料來源:By Peellden - Own work, CC BY-SA 3.0.

【請注意】上述內容經過適當簡化以適合大眾閱讀,與產業現狀可能會有差異,若您是這個領域的專家想要提供意見,請自行聯絡作者;若有產業與技術問題請參與社群討論。

【延伸閱讀】其他詳細內容請參考「積體電路與微機電產業,全華圖書公司」。<我要買書>