文章內容

打線封裝(Wire bonding)

請自行調高解析度

❒ 打線封裝的製作流程

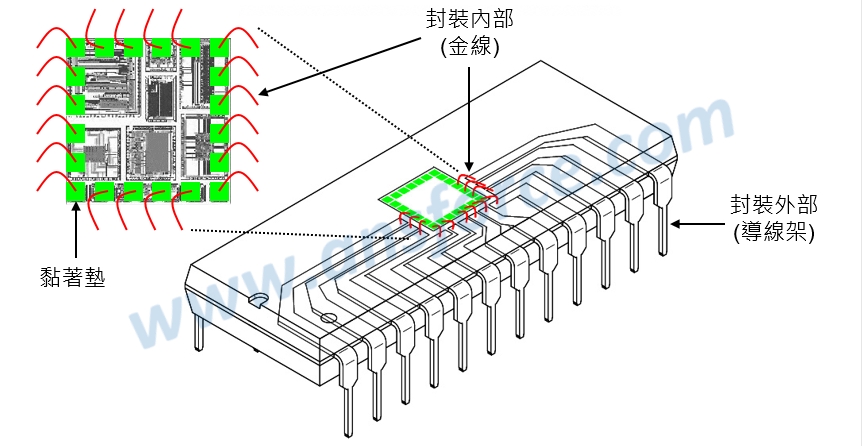

打線封裝一般都使用「導線架」與「金線」,而且必須將黏著墊(Bond pad)製作在晶片的四周圍,導線架的金屬接腳(蜈蚣腳)也必須製作在積體電路封裝外殼的四周圍,如<圖一>所示,因此打線封裝的接腳數目不能太多。打線封裝的步驟為:在靠近晶片的一側,以機械鋼嘴將金線加壓加熱打在晶片四周圍的「黏著墊」上;在靠近導線架的一側,以機械鋼嘴將金線加壓加熱打在「導線架」上,打完第一根金線,再打第二根,依此類推。

圖一 打線封裝技術。

打線封裝最大的缺點是打線的動作必須「一根一根地」完成,非常費時;而且晶片上的黏著墊與導線架的金屬接腳只能製作在四周圍,所以當晶片上的CMOS數目愈多,傳送的電訊號愈多,需要的金線也愈多,但是晶片的四周圍空間有限,只能容納固定數量的「黏著墊」,封裝外殼的四周圍空間也有限,只能容納固定數量的「金屬接腳」,因此打線封裝接腳數目不能太多。知識力www.ansforce.com。

❒ 打線封裝的應用

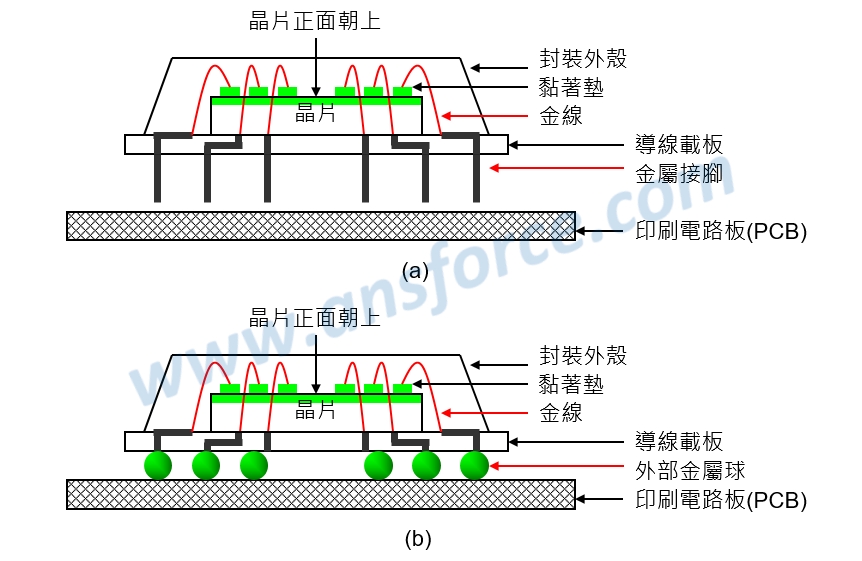

打線封裝除了可以使用「導線架」之外,也可以使用「導線載板」,如<圖二>所示,配合封裝外部使用針格陣列(PGA)或球格陣列(BGA)如下:

➤內部打線封裝,外部針格陣列(PGA):如<圖二(a)>所示,是以前英特爾(Intel)的中央處理器(CPU)常用的封裝方式,目前內部大都已經改用覆晶封裝了。

➤內部打線封裝,外部球格陣列(BGA):如<圖二(b)>所示,是以前個人電腦的北橋晶片與南橋晶片經常使用的封裝方式,目前內部大都已經改用覆晶封裝了。知識力www.ansforce.com。

圖二 打線封裝的應用。

❒ 打線封裝的優缺點

➤優點:適合中小型晶片,大型晶片也有使用,技術較成熟。

➤缺點:每支接腳必須打線封裝速度較慢,封裝體積較大。

【請注意】上述內容經過適當簡化以適合大眾閱讀,與產業現狀可能會有差異,若您是這個領域的專家想要提供意見,請自行聯絡作者;若有產業與技術問題請參與社群討論。

【延伸閱讀】其他詳細內容請參考「積體電路與微機電產業,全華圖書公司」。<我要買書>